【DK-SI-5SGXEA7N】Transceiver Signal Integrity,Stratix V GX

- 产品型号: DK-SI-5SGXEA7N/S5GSI(Part No:T0118)

- 产品品牌: TERASIC友晶科技/Intel FPGA

- 产品规格: Stratix V GX FPGA:5SGXEA7N2F40C2N

- 产品价格: 44,955

- 咨询热线:027-87538900

The Altera® Stratix® V GX Transceiver Signal Integrity (SI) Development Kit provides a platform for electrical compliance testing and interoperability analysis. The accessibility to multiple channels allows for real-world analysis as implemented in the system with transceiver channels available through SMA and popular backplane connectors. You can use this development kit to perform the following tasks:

- Evaluate transceiver link performance from 600 Mbps to 12.5 Gbps

- Generate and check pseudo-random binary sequence (PRBS) patterns via a simple to use GUI (does not require the Quartus® II software)

- Access advanced equalization to fine tune link settings for optimal bit error ratio (BER)

- Perform jitter analysis

- Verify physical medium attachment (PMA) compliance to 10GbE, 10GBASE-KR, PCI Express® (PCIe®)(Gen1, Gen2, and Gen3), Serial RapidIO®, Gigabit Ethernet, 10-Gigabit Ethernet XAUI, Common Electrical I/O (CEI) 6G, CEI-11G, high-definition serial digital interface (HD-SDI), Interlaken, and other major standards

-

Use the built-in high speed backplane connectors to evaluate custom backplane performance and evaluate link BER

Featured device

- 5SGXEA7N2F40C2N

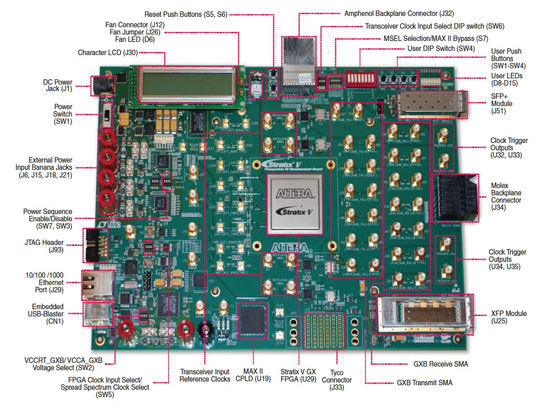

Configuration status and set-up elements

- JTAG

- On-board USB-BlasterTM

- Fast passive parallel (FPP) configuration via MAX® II device and flash memory

- Two configuration file storage

- Temperature measurement circuitry (die and ambient temperature)

Clocks

- 50 MHz, 125 MHz, programmable oscillators (preset values: 624 MHz, 644.5 MHz, 706.25 MHz, and 875 MHz)

- SMA connectors for supplying an external differential clock to transceiver reference clock

- SMA connectors for supplying an external differential clock to the FPGA fabric

- SMA connectors to output a differential clock from the FPGA's phase-locked loop (PLL) output pin

General user input/output

- 10-/100-/1000-Mbps Ethernet PHY (RGMII) with RJ-45 (copper) connector

- 16x2 character LCD

- One 8-postion dipswitch

- Eight user LEDs

- Four user pushbuttons

Memory devices

- 128-megabyte (MB) sync flash memory (primarily to store FPGA configurations)

High speed serial interfaces

-

Seven full-duplex transceiver channels routed to SMA connectors

- Short trace routed on a micro-strip

- Six strip-line channels from the with all the trace lengths are matched across channels

-

21 full-duplex transceiver channels routed to backplane connector

- Seven channels to Molex® Impact® connector

- Seven channels to Amphenol® XCede®

- Seven channels to footprint of Tyco Strada® Whisper® (connector is not populated)

Power

- Laptop DC input

- Voltage margining

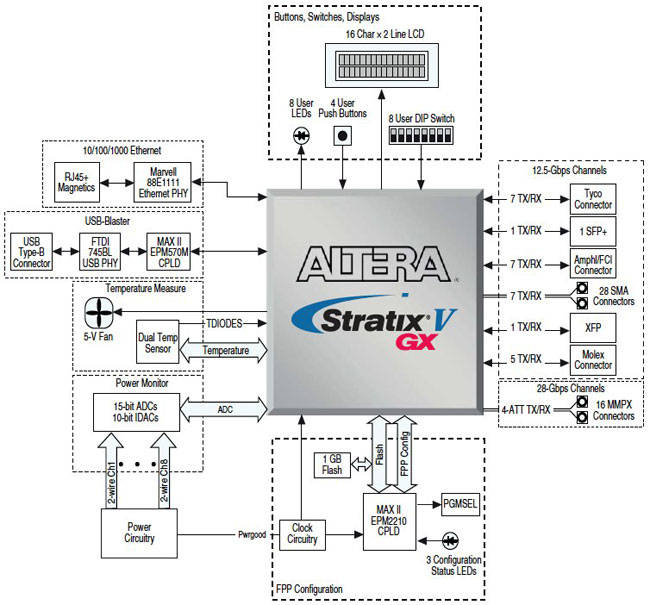

Stratix V GX Transceiver Signal Integrity Development Board Block Diagram

| No | 产品名称 | 售价(RMB) |

|---|---|---|

| 1. |

[S5GSI] Altera Transceiver Signal Integrity Development Kit, Stratix V GT Edition

产品编号: T0118

重量: 4,000g 重量: 4,000g |

¥44,955 |

Documents

CD-ROM

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| Kit installation (for boards with ES silicon) | 11.1.2 | 2013-01-03 |

|

|

| Kit installation | 12.0 | 2013-01-03 |

|