热点资讯

- Intel FPGA|如何挑选TERASIC友晶DE系列FPGA板卡?

- 资源|英特尔® Quartus® Prime设计软件的“后浪”来啦!

- Intel FPGA|如何挑选TERASIC友晶MAX 10系列FPGA板卡?

- 教育部中南地区电子电气基础课教学研究会

- 普源精电2024夏季新品发布会

- Intel FPGA|如何挑选TERASIC友晶Stratix 10系列FPGA板卡?

- 贺中国地质大学电子类测试分析仪器项目中标

- 2018 年友晶科技产学合作协同育人项目

- Intel FPGA|如何挑选TERASIC友晶Cyclone V系列FPGA板卡?

- 集美大学《高级FPGA综合实验系统》完成交付验收

咨询热线:

18062095810

邮件: wangting@whhexin.com

电话:027-87538900

地址: 湖北·武汉·鲁巷·华乐商务中心1006

Terasic友晶DE5a-Net-DDR4开发板 FAQ 集锦

DE5a-Net-DDR4

FAQ集锦

》》》

》》》

》》》

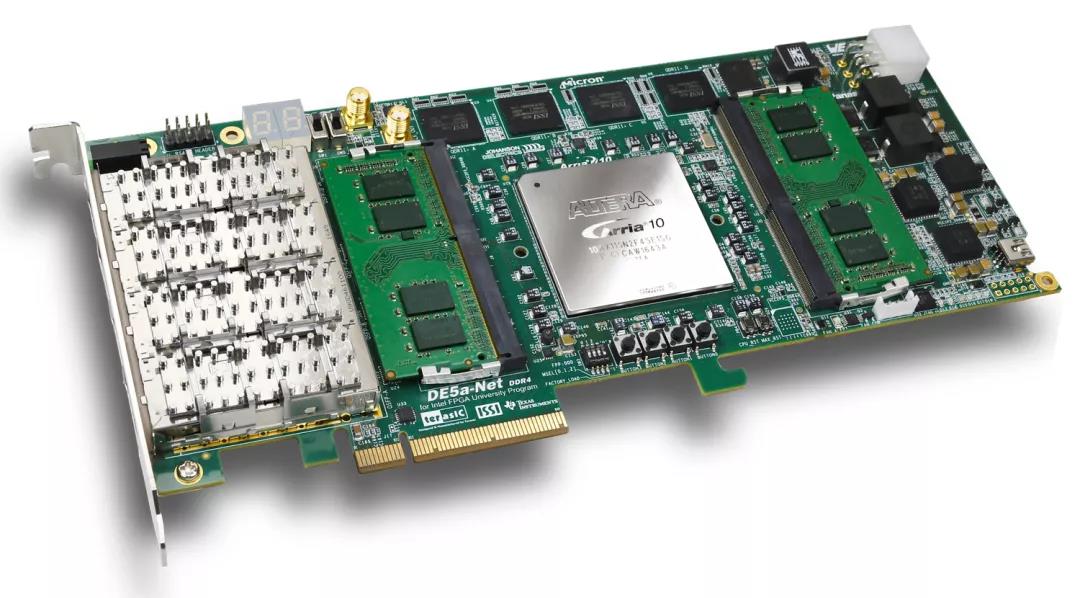

Terasic DE5a-Net-DDR4 FPGA 开发板为那些需要大容量、高带宽的内存接口,超低延迟的通信传输以及高电源效率的设计提供了理想的硬件解决方案。作为一个全高,3/4标准长度的开发板,DE5a-Net-DDR4的设计满足最苛刻的高端应用,配备Intel Arria 10 FPGA顶级芯片,完全支持低延迟交易、云计算、高效能计算、数据采集、网络处理和信号处理等高强度的应用,为业界提供最佳的系统级集成和灵活性设计。

为方便大家更好得使用这块具有强大功能的开发板,小编整理了 DE5a-Net-DDR4 FAQ 集锦,供大家参考~

NO.1

DE5a-Net-DDR4 开发板上FPGA的功耗该如何测试呢?

DE5a-Net-DDR4 开发板上集成了 power monitor (电源监测)芯片,可以用来监测开发板上FPGA的实时功率 。

您只需运行 DE5a-Net-DDR4 SystemCD\Demostrations\NIOS_BASIC_DEMO\demo_batch\ 目录下的 NIOS_BASIC_DEMO.bat 文件, 即可监测当前 FPGA 的实时功耗。详细测试步骤可以参考 DE5a-Net-DDR4 User Manual。

NO.2

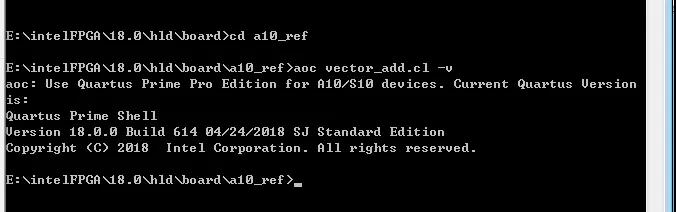

关于 DE5a-Net-DDR4 的 OpenCL 开发,对 Host 端软件环境有哪些要求?

如果您仅仅只是在 FPGA 平台上运行 OpenCL,Host 的环境只需要安装 Intel FPGA Runtime Environment for OpenCL 环境,即选择安装 Pro 版本和 Standard 版本都可以。

但是如果您需要编译 OpenCL kernel,就必须安装包含 Quartus Prime Pro 软件的 Intel FPGA SDK for OpenCL 的完整环境。

NO.3

在虚拟机上按照文档 DE5ANET_DDR4_OpenCL_BSP_17.1 来编译 "hello word" 不成功,但是编译“aoc emulator”却可以成功 ,这是为什么呢?

因为 Opencl SDK 不支持虚拟机。您在虚拟机上通过仿真模式编译 “aoc emulator” 成功,而且编译时间很短,有时甚至只需几分钟,这是因为 emulator 并没有真正意义上的编译硬件,而只是通过软件模拟。

NO.4

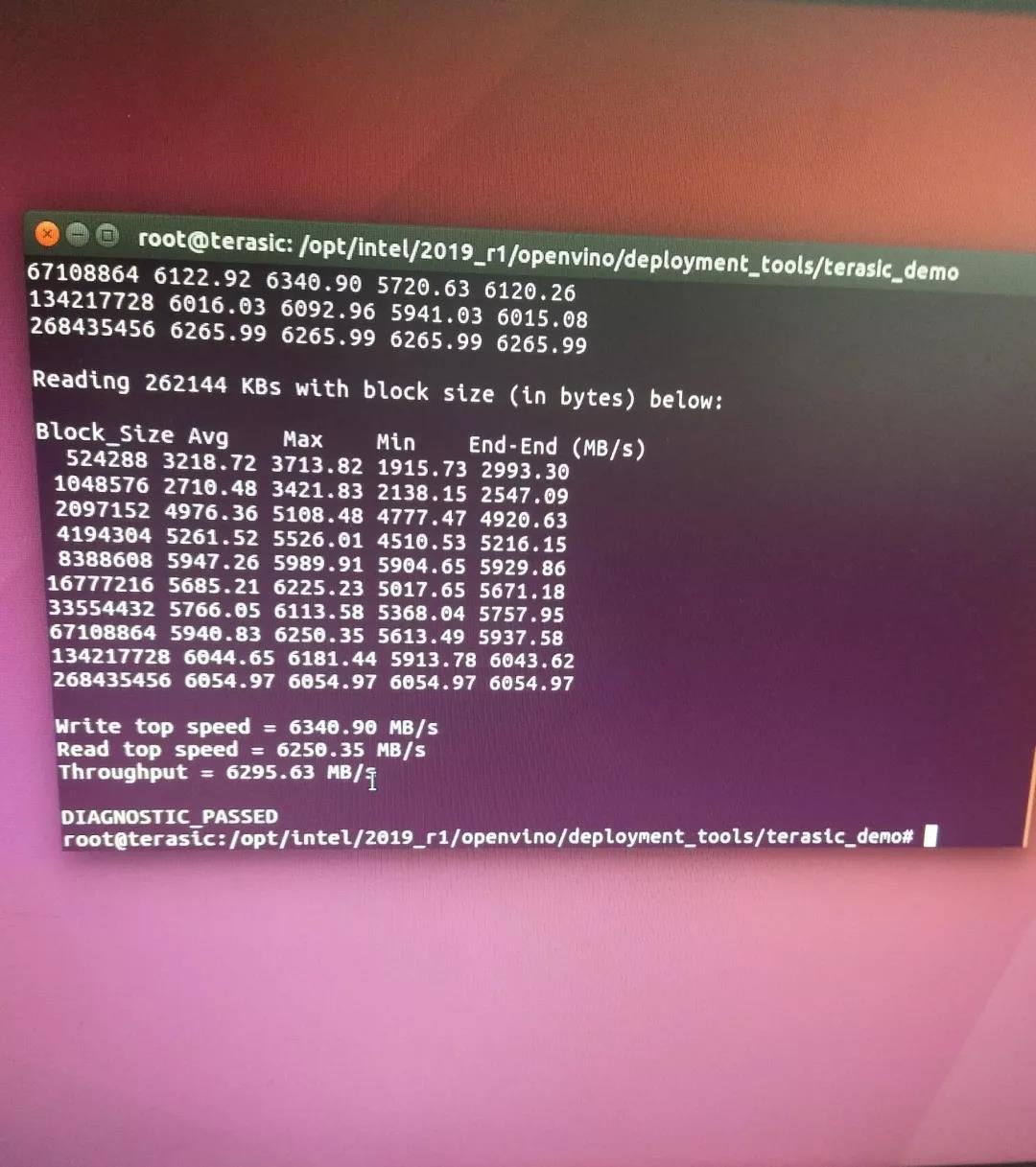

DE5a-Net-DDR4 板卡的 PCIe 速率能达到多少呢?能否介绍下具体的测试方法和流程呢?

PCIe 的速度与实际运行的 OS、PCIe Driver 及 APP 都有关系。

如果拿目前友晶官网发布的 OpenCL 包来测试的话,当 OpenCL 运行后,使用命令 “aocl diagnose acl0” 来测试 PCIe 速度,可以看到:PCIe 与 DDR4 协同工作时的速度在 6GB/s 左右。

NO.5

每次在 PC 机 和 DE5a-Net-DDR4 板卡断电后,重新启动时不能识别到 FPGA 板卡,但是运行bring_up文件夹下的 "sh test.sh" ,再重启 PC 机后就可以正常识别,请问这是不是正常现象呢?如果是,是否意味着每次断电重启都需要运行 test.sh 文件来识别 FPGA 板卡?

FPGA 默认 code 里面是没有 PCIE code 的,所以需要运行 test.sh 文件,将包含 PCIE code 的 .sof 文件烧写进 FPGA,重启之后 PC 机才能找到 PCIE 设备。但这种方法的弊端是:关电后,配置文件不能被保存,所以每次关电重启都需要再次配置 FPGA。

因此,您可以用 “aocl flash” 命令将 bitstream 烧写进板卡上的 FLASH 器件,这样每次开机时, FPGA 开发板就会默认从FLASH 启动带有 PCIE 的 code,具体方法可以参考 OpenCL 手册。

NO.6

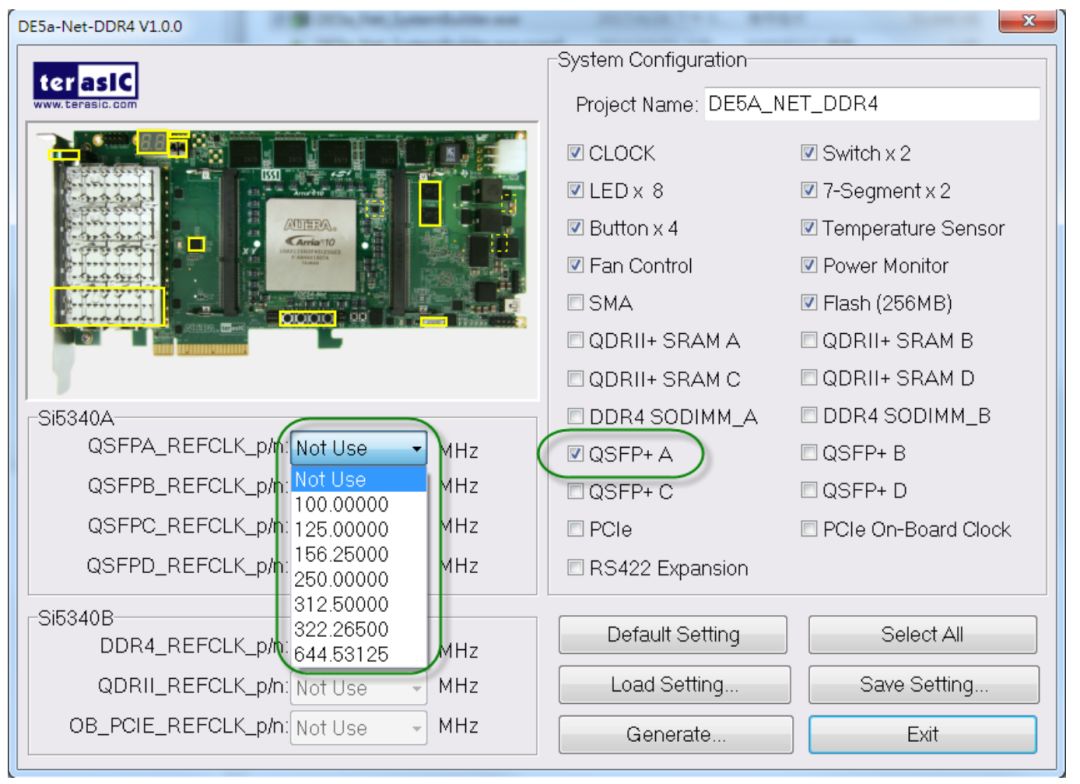

DE5a-Net-DDR4 开发板上的两个 Si5340时钟发生器可以产生的时钟范围是多少呢?应该如何配置来产生自己所需的时钟呢?

DE5a-Net-DDR4 开发板上的两个 Si5340时钟发生器可以为开发板上 QSFP, QDRII, DDR4 及 PCIe 等接口提供频率可调节的参考时钟,频率范围在 100Hz ~ 712.5Mhz 之间。

为了方便客户建立工程,Terasic 给用户提供了 System Builder 工具,在 System Builder 预设了几组常用的时钟频率,您可以直接生成进行使用(如下图);

如果预设值不是您所需的频率,您还可以通过 ClockBuider Pro 软件来生成自己所需的频率值。详细配置方法,可以参考DE5a-Net-DDR4 User Manual。