【DK-SI-5SGTMC7N】Altera Transceiver Signal Integrity Development Kit, Stratix V GT Edition

- 产品型号: DK-SI-5SGTMC7N/S5GT[T0119]

- 产品品牌: TERASIC友晶科技/ALTERA

- 产品规格: 5SGTMC7K3F40C2NES

- 产品价格: 116,955元

- 咨询热线:027-87538900

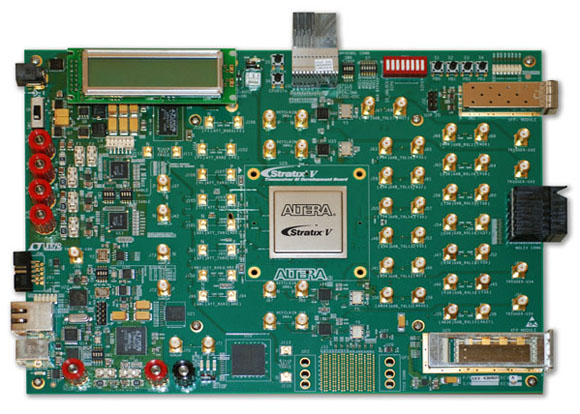

Altera® Stratix® V GT收发器信号完整性(SI)开发套件为电信号兼容性测试和互操作性分析提供了平台。您可以对多个通道进行实际分析,通过SMA以及流行的背板连接器使用在系统中实现的这些收发器通道。采用这一开发套件,您能够完成以下任务:

评估性能高达28 Gbps的收发器链路通过使用方便的GUI (不需要Quartus® II软件)来生成并检查伪随机二进制序列(PRBS)码型

使用高级均衡功能,精细的调整链路设置,降低误码率(BER)。

进行抖动分析

采用Stratix V GT FPGA,针对目标协议,验证物理介质附加(PMA)子层的互操作性,例如,CEI-25/28G、CEI-11G、PCI Express® (PCIe®) Gen 3.0、10GBASE-KR、万兆以太网、XAUI、CEI-6G、Serial RapidIO®、HD-SDI,等。

使用内置高速背板连接器评估定制背板性能以及链路BER

产品规格

安装的器件:5SGTMC7K3F40C2NES

配置、状态和设置单元

JTAG

板上USB-BlasterTM

通过MAX® II器件和闪存进行快速被动并行(FPP)配置

两个配置文件存储

温度测量电路(管芯和环境温度)

时钟

50MHz、125MHz可编程振荡器(预设值:624 MHz、644.5 MHz、706.25MHz、875 MHz)

SMA连接器,为收发器参考时钟提供外部差分时钟。

SMA连接器,为FPGA架构提供外部差分时钟。

SMA连接器,用于从FPGA的锁相环(PLL)输出引脚输出差分时钟。

通用用户输入和输出

10-/100-/1000-Mbps以太网PHY (RGMII),提供RJ-45 (铜)连接器。

16x2字符LCD

一个8位DIP开关

8个用户LED

4个用户按键

存储器件

128-megabyte (MB)同步闪存(主要用于存储FPGA配置)

高速串行接口

4个与MMPX连接器连接的全双工GTB (25.8 Gbps)收发器通道

7个与SMA连接器连接的全双工GTB (12.5 Gbps)收发器通道

连接微带线的短走线

6个带状线通道,通道间所有走线长度均匹配。

21个与背板连接器连接的全双工GXB收发器通道

与Molex® Impact®连接器连接的7个通道

与Amphenol® XCede®连接的7个通道

与Tyco Strada® Whisper®(没有安装连接器)引脚连接的7个通道

电源

笔记本计算机直流输入

电压余量

Stratix V GT收发器SI开发套件软件组成

Altera完整的设计套装(从Altera下载中心下载)

Quartus II软件为Stratix V FPGA提供支持

含一年许可

Nios II嵌入式设计套装

MegaCore®知识产权(IP)库包括PCI Express、三速以太网、SDI和DDR3高性能控制器MegaCore IP内核

通过OpenCore Plus进行IP评估

含一年许可

Nios II嵌入式设计套装

MegaCore®知识产权(IP)库包括PCI Express、三速以太网、SDI和DDR3高性能控制器MegaCore IP内核

通过OpenCore Plus进行IP评估

电路板更新入口

提供Nios II网络服务器,支持系统远程更新。

基于GUI的电路板测试系统

通过JTAG与PC连接

用户控制的PMA设置(预加重和均衡,等)

状态指示(误码,BER,等)

完整的文档用户控制的PMA设置(预加重和均衡,等)

状态指示(误码,BER,等)

用户指南

参考手册

电路板原理图和布板设计文件

Stratix V GT收发器SI开发套件

Documents

CD-ROM

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| Kit installation (for boards with ES silicon) | 11.1.2 | 2013-01-03 |

|

|

| Kit installation | 12.0 | 2013-01-03 |

|