热点资讯

咨询热线:

18062095810

邮件: wangting@whhexin.com

电话:18062095810

地址: 湖北·武汉·鲁巷·华乐商务中心1006

PCI-SIG协会发布PhyTest Spec,指出PCIe5测试无需同时捕获数据和时钟

泰克科技

PCIe官方组织PCI-SIG协会在2020年2月27日发布了PCIe Gen5的首版Phy Test Spec规范V0.3,其中列举了PCIe Gen5的System和Addin Card物理层测试所需的测试项,特别需要强调的是,规范明确指出PCIe Gen5 System发送端测试将不再使用双端口(Dual-port)的方式进行,不再需要将data和clock同时接入示波器进行测试!

规范原文: “Dual-port method where clock and data is captured simultaneously will no longer be supported for 32GT/s.”

这就意味着,PCIe Gen5测试只需要将数据单独接入示波器进行测试,只需要用到两个高带宽通道即可,而不是像某仪器厂商臆测并大肆宣传的那样必须使用4通道50GHz示波器才能进行Gen5测试!这对广大PCIe5设计者来说无疑是一个福音,升级设备所需预算大幅降低,Gen5测试变得触手可及。

▼ ▼ ▼

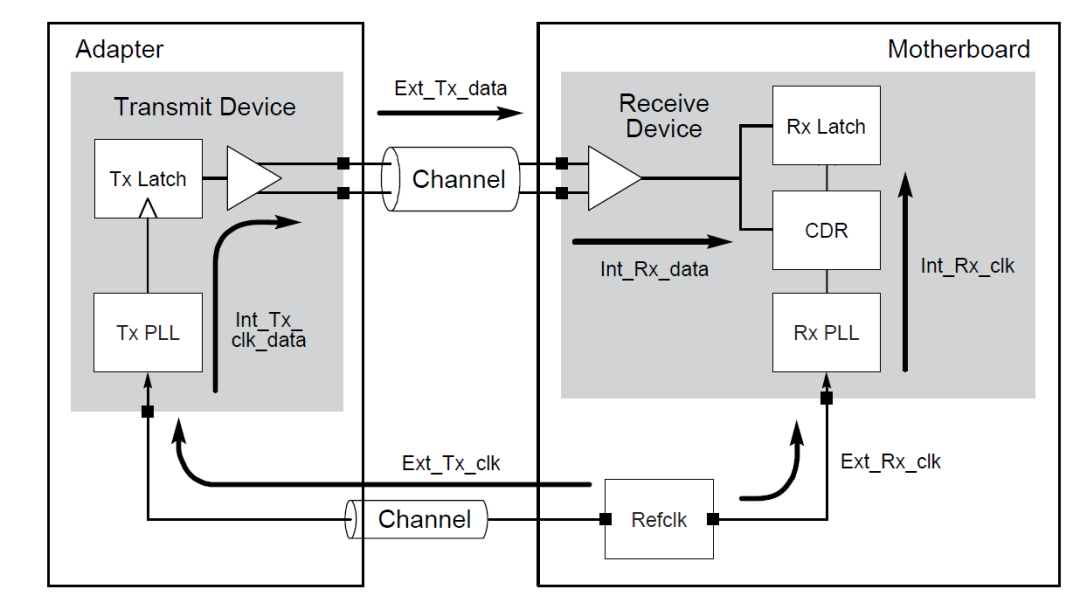

这种测试方法最早提出是在PCIe Gen2。为了测试System而专门引入的 - Addin Card则一直都只需要采集Data即可。Dual-Port测试的时候需要将数据和时钟同时引入示波器中,然后用Intel提供的测试工具Sigtest进行分析,得到最终测试结果。

Sigtest使用规范要求的最小/最大的锁相环带宽&Peaking , 将100MHz Clock倍频到与Data同速率(如5GHz/8GHz/16GHz),然后应用不同的相位对齐参数将Data对齐倍频后的Clock,计算出所有这些组合里最恶劣的眼图和抖动指标。

Dual-Port在最新Gen5中被移除?

PCIe Gen2引入Dual-Port测量方法在当时是有其现实意义的,这种测试也延续到了Gen3和Gen4,但随着技术的发展,这种设计在Gen5已经不再有价值,因此在最新的Gen5 Phy Test Spec中被移除。规范做出这个决定是经过讨论研究后慎重决定的,我们挑其中的两点原因来简单谈谈:

PCIe Gen2 CDR能力有限,对于33KHz-2MHz范围内的低频抖动 (典型例子就是SSC扩频时钟)的抑制能力很弱。对于带SSC的System待测物,需要将数据和时钟同时捕获、互相参考才能得到准确的测量结果。而到了Gen5,无论是Common Clock还是SRIS架构都可以很好的抑制低频抖动,不再需要参考System提供的100MHz时钟。

PCIe2 Gen2的时钟规范是很宽松的,其抖动有效值小于3.1ps即可。如果System提供的100MHz参考时钟较差,数据参考时钟后测出的眼图和抖动也会较差,因此在评估Data信号质量时同时采集并对齐100MHz参考时钟就很有必要。而到了Gen5,对Clock的品质要求大大提高,时钟抖动有效值要求低至0.15ps,近乎理想时钟。数据眼图和抖动测量时使用参考时钟或使用软件算法时钟已经没有什么区别了,只需对时钟进行单独的测量以确保其品质就可以了。

除了只需要两通道就可以测量PCIe5这一大好消息之外,V0.3版PCIe Phy Test Spec 还明确列举了Gen5的测试项,这些测量项的定义和Gen4相比没有什么大的改变。

Electrical Compliance, Preset, Transmitter / Receiver Lin Equalization, 以及Addin Card专属的Pulse Width, Initial TxEQ, PLL Bandwidth等测量项都在Gen5里继承下来了。

规范中还提到了一些新的变化,比如AC Based Preset测试方法,将取代Gen1-4所使用的DC Based测量方法;新的System/Addin Card接收机校准流程后续将会推出, Gen5测试夹具的详细规格指标后续将会推出。

泰克PCIe物理层规范测试方案

泰克科技拥有业内完备的PCIe物理层规范测试方案,一直是行业内的佼佼者。早在2019上半年,泰克专家Dan Froelich曾在TIF和开放实验室系列活动中,已经为中国广大的客户普及了PCIe Gen5测试的概念和初步方法。

泰克科技公司旨在紧随PCIe技术发展的进程,同步发布相关的测试方案,力求为客户提供正确、及时的测试测量手段,确保顺利进行PCIe一致性测试及调试。

请保持对泰克科技的关注,我们也将在第一时间推送最新的PCIe测试技术的发展和演进。

注:Dan Froelich和David Bouse曾是Intel在PCI-SIG的重要代表,Dan Froelich是PCI-SIG 测试规范制定工作组Serial Enabling Workgroup 前主席, David Bouse是PCIe Gen4 PHY Test Spec的第一作者。

“诚实守信”是我们遵循的原则,

“优质服务”是我们对用户的承诺

欲知更多产品和应用详情,您还可以通过如下方式联系我们:

邮箱:1569945049@qq.com

电话:027-87538900/18672326195(郑先生)

什么叫Dual-port测试方法?