热点资讯

- Intel FPGA|如何挑选TERASIC友晶DE系列FPGA板卡?

- 资源|英特尔® Quartus® Prime设计软件的“后浪”来啦!

- Intel FPGA|如何挑选TERASIC友晶MAX 10系列FPGA板卡?

- 教育部中南地区电子电气基础课教学研究会

- 普源精电2024夏季新品发布会

- Intel FPGA|如何挑选TERASIC友晶Stratix 10系列FPGA板卡?

- 贺中国地质大学电子类测试分析仪器项目中标

- 2018 年友晶科技产学合作协同育人项目

- Intel FPGA|如何挑选TERASIC友晶Cyclone V系列FPGA板卡?

- 集美大学《高级FPGA综合实验系统》完成交付验收

咨询热线:

18062095810

邮件: wangting@whhexin.com

电话:027-87538900

地址: 湖北·武汉·鲁巷·华乐商务中心1006

后摩尔定律如何创新?把握这两关键点将激发“洪荒之力”

超大数据量为现代计算带来了众多复杂的挑战,这其中,FPGA扮演着非常关键的角色。FPGA 设计面临的一个严峻挑战是:集成哪些组件,以及集成时放弃哪些组件?灵活性至关重要。上述问题不仅关乎芯片内部,还关乎系统层面,同样,也影响着众多开发者所依靠的开发工具。其实,早在1965年,戈登·摩尔就已洞悉到芯片级异构集成将引领未来发展。异构集成可简单分为三个层级:芯片层级(器件层级)的异构集成、系统层级的异构集成、软件层级的异构性。所有三个层级的异构性带来系统的可重配置性。

如今,异构集成的价值日益突出,它不仅能够缩小总体外形,还能降低功耗,在性能得以提升的同时,使接口也能够进行更好的优化。在系统内部的多个层级都可以选择采用这种技术,最典型的是借助封装技术、所拥有的接口以及开发工具完成大量工作和任务。

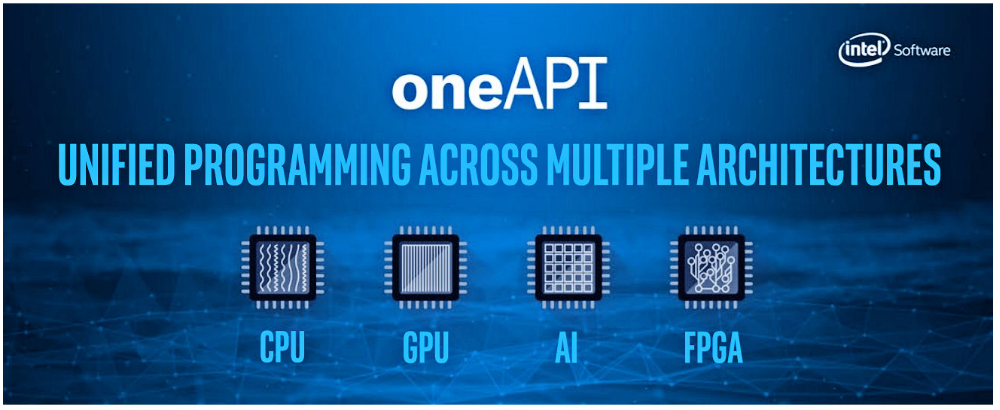

英特尔目前正朝这一方向努力:使用高级封装将公司的所有技术整合到一个 IC 封装中。具体而言,在芯片层级开发高级封装技术,在系统层级整合多种处理架构,在软件层级推出 oneAPI 计划、英特尔 oneAPI 统一编程环境和 Data Parallel C ++ 编程语言。

出色的硬件技术是一切的基础

异构设备设计需要 FPGA 方面的创新,但前提是具备出色的 FPGA 技术。所有 FPGA 厂商都在努力构建最出色的 FPGA 结构,并根据该结构进行相应的创新。例如,FPGA 的基本逻辑与计算架构如何与内存协同工作?FPGA 的一个主要优势是其片上内存,它对于 AI 和机器学习 (ML) 尤为重要。出于性能的原因,厂商需要将 AI/ML 集成到 FPGA 封装的内存中。

另一个创新领域是互连,无论是异构互连,还是为解决 TDP 和功耗问题而采用的封装设计。去年,英特尔将高级总线接口 AIB 规范引入开源领域,CHIPS 联盟等行业组织正在推动将 AIB 规范作为一项开放式行业标准,以促进芯片间连接,启动 chiplet 生态系统。目前,该接口已应用于英特尔® Agilex™ FPGA 和英特尔® Stratix® 10 FPGA 。

工艺技术同样极其重要,工艺节点的组合可支持您轻松组合定制 IP、标准 IP、灵活 FPGA IP 和互连 IP,从而为您提供最多的设计选择。在设计时,您只需要将部分功能放在最先进的工艺节点上。部分功能,尤其是 I/O 功能,无法充分利用最先进的工艺节点。模拟功能和内存无法使用最先进的工艺节点。这也是异构设备设计与制造的优势所在,它可以支持您进行不同的设计权衡——例如在静态功耗方面——对于每个新器件的设计,功耗都至关重要。在英特尔,我们一直努力在功耗和性能这两个方面实现平衡。

统一的软件开发环境发挥异构计算潜力

现在,有了异构集成的硬件FPGA支持,我们又该如何统一进行开发呢?由于市场中不存在万能的产品,为了取得成功,您必须集成各种计算架构,然后通过通用软件框架为其提供支持。

当今大多数程序员在解决工作负载问题时,不需要了解 FPGA 的内部结构或相关的其他任何计算元件。他们只想了解编程模型。他们关心的是,编程模型是否支持编写 C 代码并进行编译?他们希望完全照搬标准 C++ 开发环境与编译器模式:编译与加载程序,然后就可以正常运行了。

英特尔相信开放的方法是解决异构开发难题的关键。问题在于:我们如何在解决该难题的同时,按既定用途使用开放的概念?可以从以下 4 个关键要素着手解决该问题:

第一个要素是语言的选择。如果目标开发人员是一位 C++ 程序员,那么显然,包含太多厂商专属语言扩展或特定编码风格的任何语言都不算是真正的开源解决方案。您需要从行业标准入手,例如 C++ 或来自 Khronos Group 的 SYCL。英特尔推荐使用 Data Parallel C++ 增强 SYCL。

其次,您需要为开发工具提供一个集成环境。独立的编译器接受使用标准语言编写的程序,并输出厂商专用的 FPGA 比特流,这对传统 C 程序员仍不够。您需要一个集成系统,以便在易用性和性能之间取得适当的平衡。您无法同时获得最高性能和全部的易用性,因此,您需要一个包含调试器、性能分析器、advisor 和优化器的集成设计环境。将语言集成至全面的开发环境是第二个关键因素。英特尔® oneAPI 统一编程模型提供了跨多个架构(包括 CPU、GPU、FPGA 和加速器)的统一 IDE 环境。

第三个要素是拥有真正开放的解决方案及开放的社区。您需要为整个异构计算平台构建一个开放的生态系统。英特尔的方法是推出全新 oneAPI 计划,并邀请所有人加入该计划。

第四,在架构层面,从异构硬件集成的角度来看,您需要慎重决策,以加速工作负载。例如,您的内存接口类型和计算机元件之间的互连将从根本上改变编译器行为及其优化。影响性能的另一个因素是将代码分割成加速内核,而不是将工作负载代码保存在 CPU 主机上。我们不能只考虑软件。我们必须考虑到一系列异构硬件(包括作为异构工作负载目标的互连),才能发挥异构计算的全部潜力。

两大异构集成“模范生”分析,性能突破与挑战共存

现在英特尔已经可以有效地设计和制造异构器件。例如,当前的英特尔® Agilex™ FPGA 和英特尔® Stratix® 10 FPGA 均属于异构 FPGA。我们在这两款 FPGA 中集成了 HBM2 堆叠芯片 DRAM。我们在 tile(或 chiplet)上放置了面向这些英特尔 FPGA 的高速串行收发器,以便以太网和 PCIe 协议与 FPGA 结构的设计相分离。FPGA 结构对迁移至新制程节点有利,但接口不能。借助异构设计方法,英特尔能够跨所有节点在 FPGA 结构和 I/O 接口两方面分别实现创新。我们可使用多个节点以最佳的方式构建复杂器件。

虽然如此,我们仍然面临诸多挑战。第一个挑战是 TDP,即热设计功耗。封装中的功能越多,散热越难。除了散热之外,业务模式也面临着挑战,进而演变为复杂的商业问题。一旦有两家或两家以上的公司将其 IP 放在同一个器件中,业务模式就会更加复杂。例如,基于不同厂商技术的异构器件如何上市?这些只是其中的一部分挑战。尽管如此,许多厂商依然正在加快设计和制造异构器件。