产品展示

-

- Intel FPGA-Altera Agilex母板 Intel FPGA-Altera Stratix母板 Intel FPGA-Altera Arria母板 Intel FPGA-Altera Cyclone母板 Intel FPGA-Altera MAX母板 Intel FPGA-Altera 多媒体子板 Intel FPGA-Altera 界面转换子板 Intel FPGA-Altera 影像显示类子板 Intel FPGA-Altera 网路子板 Intel FPGA-Altera 类比/数位转换子板 Intel FPGA-Altera RF子板 Intel FPGA-Altera机器人套件 Intel FPGA-Altera USB Blaster Intel FPGA-Altera配件 FPGA|DSP|ARM|EDA|SOC教学实验箱 TI系列-C6000 DSP|ARM TI系列-C5000 DSP TI系列-C2000 DSP TI系列-DaVinci|Sitara TI系列-仿真器

推荐产品

- FPGA综合实验台 HC-STD-M

- 【DPO7254C】Tektonix泰克 高级信号分析示波器

- 【TMS320C6655/57】Tronlong创龙TL665xF-EasyEVM开发板

- HKMX-30型 十字路口交通信号灯实训装置

- 【SFP】TERASIC友晶SFP-HSM子板

- 【XAUI-SFP】DUAL XAUI TO SFP+ HSMC BOARD

- 【DK-DEV-1SGX-H-A】Intel Stratix 10 GX FPGA Development Kit

- 【TDS2024C】Tektonix泰克 200MHz示波器

- 【6221】Tektonix泰克 精密电流源

- 【DS1202Z-E】RIGOL普源 200MHz数字示波器

咨询热线:

18062095810

邮件: wangting@whhexin.com

电话:027-87538900

地址: 湖北·武汉·鲁巷·华乐商务中心1006

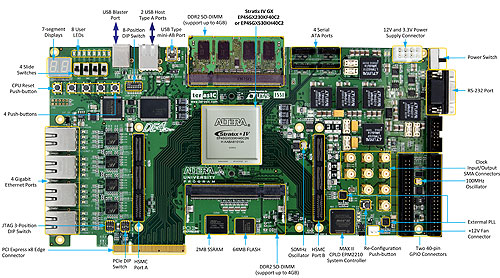

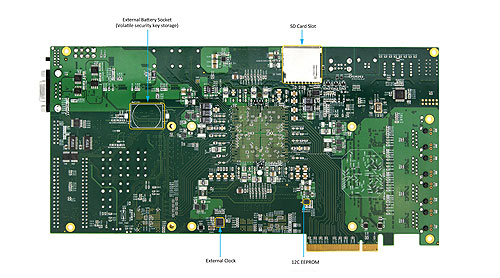

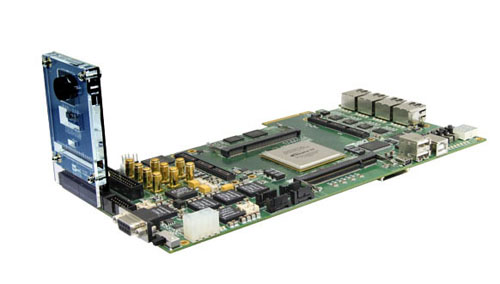

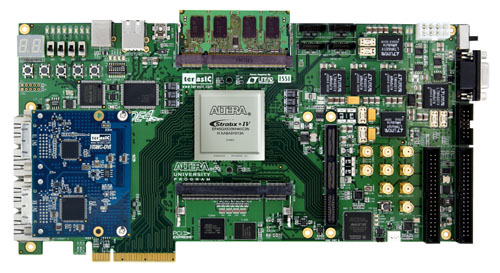

[DE4-230-C2] Altera DE4-230 Development and Education Board

- 产品型号: DE4-230-C2[P0054]

- 产品品牌: TERASIC友晶科技/Intel FPGA

- 产品规格: Stratix IV GX EP4SGX230

- 产品价格: 欢迎咨询采购,量多优惠多,提供完善的售后保障和支持!

- 咨询热线:18062095810

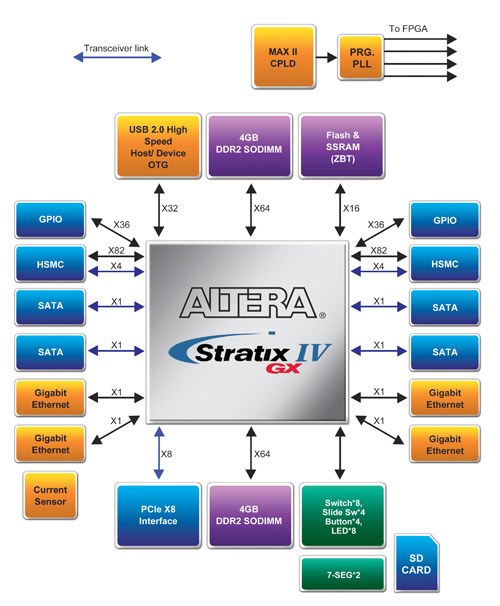

DE4 采用了 Stratix ®IV GX 芯片并支持行业标准的外围设备,连接器和界面的丰富特性适用于大范围的计算密集型应用。经过对收发器抖动性,协议兼容性和平衡性能的评估, DE4超越了 Stratix IV GX 芯片串行数据收发器标准性能,能够在 SATA 以及 HSMC 接口上以 10Gbps 速率运行。专为需求更大带宽,更低的抖动性能以及低的功耗的终端市场而设计,DE4 具有高性能、丰富串行连接以及先进存储器接口的特点,为高阶的应用需求提供了一个理想的硬件平台。

三大特点:

高速接口及扩充性:带有嵌入式收发器的 Stratix ® IV GX 的 FPGA 平台的优势在于让 DE4 与 2.0 版本的PCI Express 标准及串行 ATA(SATA)的接口充分兼容,以便能够充分利用存储应用的集成方案。集成了内置的 PCI Express SATA 收发器,可支持千兆以太网协议。DE4 也可经由两个 HSMC 连接 HSMC 子卡或者多块 DE4 互连组成自定义系统并扩充为更大规模之 ASIC 原型验证平台。

公开源码之范例:DE4 附带 13 个经过全面测试和提供支持的面向连接性的参考设计,源码完整公开。

大容量内存系统:DE4 还包含两个 DDR2 SO-DIMM 插槽,支持最大容量为 8GB 的易失性内存,并可运行在 400MHz 的时钟频率上。

DE4 开发板主要的组件模块如下:

FPGA 芯片

Stratix IV GX EP4SGX230

228,000 logic elements (LEs)

17,133K total memory Kbits

1,288 18x18-bit multipliers blocks

2 PCI Express hard IP blocks

744 user I/Os

8 phase locked loops (PLLs)

Stratix IV GX EP4SGX530

531,200 logic elements (LEs)

27,376K total memory Kbits

1,024 18x18-bit multipliers blocks

4 PCI Express hard IP Blocks

744 user I/Os

8 phase locked loops (PLLs)

FPGA 配置

JTAG and Fast Passive Parallel (FPP) configuration

内建 USB Blaster 电路

内存

64 MB Flash with a 16-bit data bus

2 MB ZBT SSRAM

I2C EEPROM

Two DDR2 SO-DIMM Sockets

400 MHz clock rate

Maximum theoretical bandwidth of over 102 Gbps

Up to 8-Gbyte capacity in total

SD Card Socket

支持 SPI 以及 SD 1-bit 两种 SD Card 读取模式

按钮,开关与 LED

4 个按钮

4 个滑动开关

8 个 LED

8 位 DIP 开关

2 个七段数码显示管

2 个独立的七段数码显示管

On-Board Clocks

3 Programmable PLLs configured via FPGA

o HSMA, HSMB transceiver clock source

o SATA reference clock

o FPGA LVDS clock input

50MHz/100MHz oscillator

SMA 接头

2 SMA connector for external transceiver clock input

4 SMA connector for LVDS clock input/output

2 SMA connectors for clock output

1 SMA connector for external clock input

4 个 SATA 接口

Support SATA 3.0 standard 6Gbps signaling rate

Two host and two device ports

4 个千兆以太网接口

Integrated 1.25 GHz SERDES

PCI Express x8 Edge Connector

Support connection speed of Gen1 at 2.5Gbps/lane to Gen2 at 5.0Gbps/lane

Connection established with PC motherboard with x8 or x16 PCI Express slot

Two 172-pins High Speed Mezzanine Card (HSMC)

2 female-HSMC connectors

I/O voltage 2.5V

Total of 12 high-speed transceivers at 8.5 Gbps

Total of 38 LVDS pair at 1.6 Gbps

两组40个接脚扩充槽

72个 I / O引脚及4个电源和接地线,拉到40-pin 扩充槽

用于40-pin 扩充槽的排线可利用 IDE 硬碟专用的40-pin 排线

I/O voltage 3.0V

USB主/从控制器

完全符合通用串行总线规范2.0修订版标准

支持数据高速传输、全速传输与低速传输

Support both USB host and device

3种USB 接口 (one type mini-AB for host/device and two type A for host)

支持PIO与DMA模

电源

DC input 12V and 3.3V

PCI Express edge connector power

Support PCI Express external standard power source

On-Board power measurement circuitry

Block Diagram

![]() MTL 接口连接示意图

MTL 接口连接示意图

MTL 与 DE4 连接示意图

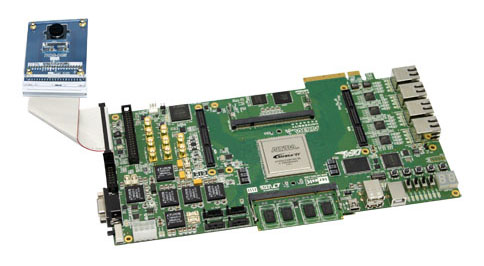

![]() D5M 接口连接示意图

D5M 接口连接示意图

D5M 与 DE4 连接示意图

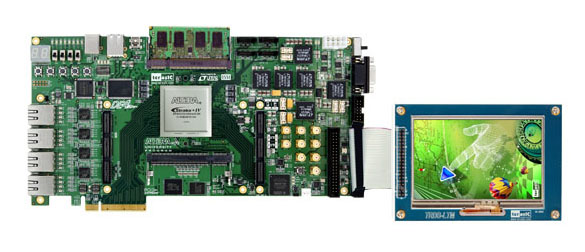

![]() LTM 接口连接示意图

LTM 接口连接示意图

LTM 与DE4 连接示意图

![]() DVI-HSMC 接口连接示意图

DVI-HSMC 接口连接示意图

DVI-HSMC 与 DE4 连接示意图

注意:若要将 DVI-HSMC 子卡连接到 DE4,HSMC 插座需要先连接两个适配器(HFM2),它是DE4套件的一部分。

![]() SFP-HSMC接口连接示意图

SFP-HSMC接口连接示意图

SFP-HSMC 与 DE4 连接示意图

![]() SDI-HSMC接口连接示意图

SDI-HSMC接口连接示意图

SDI-HSMC 与 DE4 连接示意图

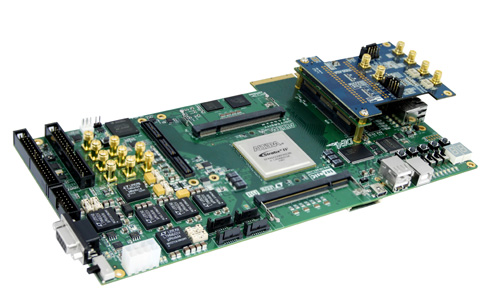

![]() ADA-HSMC 接口连接示意图

ADA-HSMC 接口连接示意图

ADA-HSMC 与 DE4 连接示意图

注意:若要将 ADA-HSMC 子卡连接到 DE4,HSMC 插座需要先连接一个适配器(HFM2),它是DE4套件的一部分。

![]() DCC-HSMC 接口连接示意图

DCC-HSMC 接口连接示意图

DCC-HSMC 与 DE4 连接示意图

注意:若要将 DCC-HSMC 子卡连接到 DE4,HSMC 插座需要先连接两个适配器(HFM2),它是DE4套件的一部分。

![]() HTG 接口连接示意图

HTG 接口连接示意图

HTG 与 DE4 连接示意图

注意:若要将 HTG 子卡连接到 DE4,HSMC 插座需要先连接一个适配器(HFM2),它是DE4套件的一部分。

![]() MSV 接口连接示意图

MSV 接口连接示意图

MSV 与 DE4 连接示意图

注意:若要将 MSV 子卡连接到 DE4,HSMC 插座需要先连接一个适配器(HFM2),它是DE4套件的一部分。

主产品订购

| No | 产品名称 | 售价(RMB) |

|---|---|---|

| 1. |

[DE4-230-C2] Altera DE4-230 Development and Education Board

产品编号: P0054  重量: 2,500g 重量: 2,500g | xxx |

| 2. |

[DE4-530-C2] Altera DE4-530 Development and Education Board

产品编号: P0058  重量: 2,500g 重量: 2,500g | xxx |

选购配件 (如需选购, 请与主产品同时订购)

| No | 配件名称 | 售价(RMB) |

|---|---|---|

| 1. |

DDR2-800 1GB 200PIN SODIMM

产品编号: MMM-3033-DSL  重量: 200g 重量: 200g | xxx |

| 2. |

DDR2-800 4GB 200PIN SODIMM

产品编号: MMM-3025-DSL  重量: 200g 重量: 200g | xxx |

| 3. |

THCB-HMF2

产品编号: S0090  重量: 300g 重量: 300g | xxx |

Download

Documents

标题

版本

档案大小(KB)

新增日期

下载

DE4_User Manual

1.4

16117

2017-03-21

CD-ROM

标题

版本

档案大小(KB)

新增日期

下载

DE4 CD-ROM

1.4.0

2017-03-21

DE4 Tools

DE4 Control Panel —— 让使用者可以借助 PC 操控 DE4 上的各个接口与组件。

DE4 Control Panel

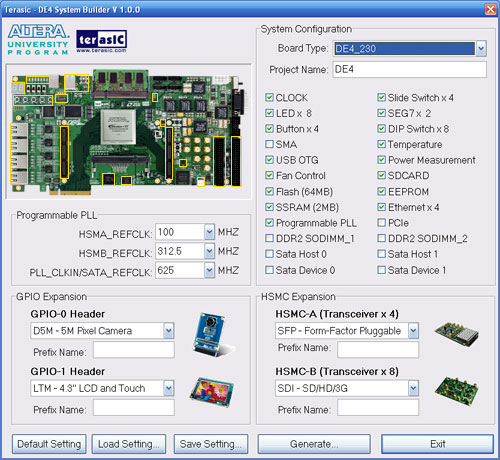

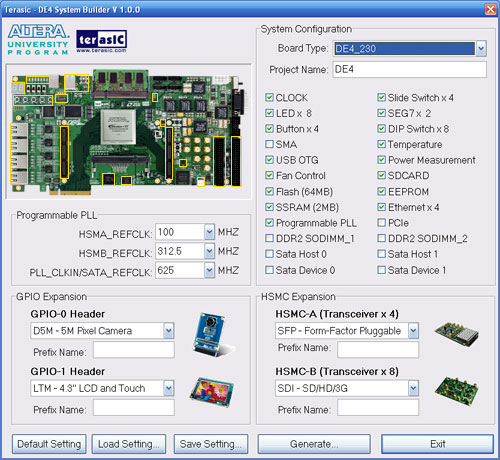

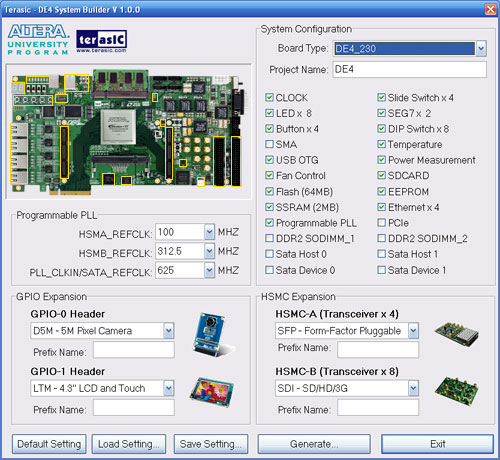

DE4 System Builder —— 专门为 DE4 开发板所设计的一套强大软件工具。这套工具可以帮助使用者轻松建立符合 DE4 开发板的 Quartus II 项目。使用者只须专注于自己的逻辑设计,DE4 System Builder 即会直接以 DE4 开发板产生相应的 top-level design file、pin assignment 以及 I/O standard 设定。除此之外,通过 DE4 System Builder 的 HSMC connectors ,你还可以选择各种与 DE4 搭配使用的子板。

DE4 System Builder

The generated Quartus II project files include the following:

Quartus II Project File (.qpf)

Quartus II Setting File (.qsf)

Top-Level Design File (.v)

External PLL Contorller (.v)

Synopsis Design Constraints file (.sdc)

Pin Assignment Document (.htm)

DE4 Demonstrations

Reference Designs

USB Host

USB Device

Ethernet – Simple Socket Server

PCIe Simple I/O Control

PCIe Image Process Application

Power Measurement

SATA Loopback

HSMC Loopback

SD Card Reader

PLL IP Configuration

DDR2 SDRAM

Web Server

Download

Documents

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| DE4_User Manual | 1.4 | 16117 | 2017-03-21 |  |

CD-ROM

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| DE4 CD-ROM | 1.4.0 | 2017-03-21 |

DE4 Tools

DE4 Control Panel —— 让使用者可以借助 PC 操控 DE4 上的各个接口与组件。

DE4 Control Panel

DE4 System Builder —— 专门为 DE4 开发板所设计的一套强大软件工具。这套工具可以帮助使用者轻松建立符合 DE4 开发板的 Quartus II 项目。使用者只须专注于自己的逻辑设计,DE4 System Builder 即会直接以 DE4 开发板产生相应的 top-level design file、pin assignment 以及 I/O standard 设定。除此之外,通过 DE4 System Builder 的 HSMC connectors ,你还可以选择各种与 DE4 搭配使用的子板。

DE4 System Builder

The generated Quartus II project files include the following:

Quartus II Project File (.qpf)

Quartus II Setting File (.qsf)

Top-Level Design File (.v)

External PLL Contorller (.v)

Synopsis Design Constraints file (.sdc)

Pin Assignment Document (.htm)

DE4 Demonstrations

Reference Designs

USB Host

USB Device

Ethernet – Simple Socket Server

PCIe Simple I/O Control

PCIe Image Process Application

Power Measurement

SATA Loopback

HSMC Loopback

SD Card Reader

PLL IP Configuration

DDR2 SDRAM

Web Server

Download

Documents

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| DE4_User Manual | 1.4 | 16117 | 2017-03-21 |  |

CD-ROM

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| DE4 CD-ROM | 1.4.0 | 2017-03-21 |

本授权条款允许使用者於使用所有友晶及 Altera 开发板时,得以重制、散布、传输以及修改友晶科技提供的源码,但不得为商业目的之使用。使用时必须於引用处表彰友晶科技 (Terasic Inc.) 之商号。

DE4 Tools

DE4 Control Panel —— 让使用者可以借助 PC 操控 DE4 上的各个接口与组件。

DE4 Control Panel

DE4 System Builder —— 专门为 DE4 开发板所设计的一套强大软件工具。这套工具可以帮助使用者轻松建立符合 DE4 开发板的 Quartus II 项目。使用者只须专注于自己的逻辑设计,DE4 System Builder 即会直接以 DE4 开发板产生相应的 top-level design file、pin assignment 以及 I/O standard 设定。除此之外,通过 DE4 System Builder 的 HSMC connectors ,你还可以选择各种与 DE4 搭配使用的子板。

DE4 System Builder

The generated Quartus II project files include the following:

Quartus II Project File (.qpf)

Quartus II Setting File (.qsf)

Top-Level Design File (.v)

External PLL Contorller (.v)

Synopsis Design Constraints file (.sdc)

Pin Assignment Document (.htm)

DE4 Demonstrations

Reference Designs

USB Host

USB Device

Ethernet – Simple Socket Server

PCIe Simple I/O Control

PCIe Image Process Application

Power Measurement

SATA Loopback

HSMC Loopback

SD Card Reader

PLL IP Configuration

DDR2 SDRAM

Web Server