产品展示

-

- Intel FPGA-Altera Agilex母板 Intel FPGA-Altera Stratix母板 Intel FPGA-Altera Arria母板 Intel FPGA-Altera Cyclone母板 Intel FPGA-Altera MAX母板 Intel FPGA-Altera 多媒体子板 Intel FPGA-Altera 界面转换子板 Intel FPGA-Altera 影像显示类子板 Intel FPGA-Altera 网路子板 Intel FPGA-Altera 类比/数位转换子板 Intel FPGA-Altera RF子板 Intel FPGA-Altera机器人套件 Intel FPGA-Altera USB Blaster Intel FPGA-Altera配件 FPGA|DSP|ARM|EDA|SOC教学实验箱 TI系列-C6000 DSP|ARM TI系列-C5000 DSP TI系列-C2000 DSP TI系列-DaVinci|Sitara TI系列-仿真器

推荐产品

- FPGA综合实验台 HC-STD-M

- 【DPO7254C】Tektonix泰克 高级信号分析示波器

- 【TMS320C6655/57】Tronlong创龙TL665xF-EasyEVM开发板

- HKMX-30型 十字路口交通信号灯实训装置

- 【SFP】TERASIC友晶SFP-HSM子板

- 【XAUI-SFP】DUAL XAUI TO SFP+ HSMC BOARD

- 【DK-DEV-1SGX-H-A】Intel Stratix 10 GX FPGA Development Kit

- 【TDS2024C】Tektonix泰克 200MHz示波器

- 【6221】Tektonix泰克 精密电流源

- 【DS1202Z-E】RIGOL普源 200MHz数字示波器

咨询热线:

18062095810

邮件: wangting@whhexin.com

电话:027-87538900

地址: 湖北·武汉·鲁巷·华乐商务中心1006

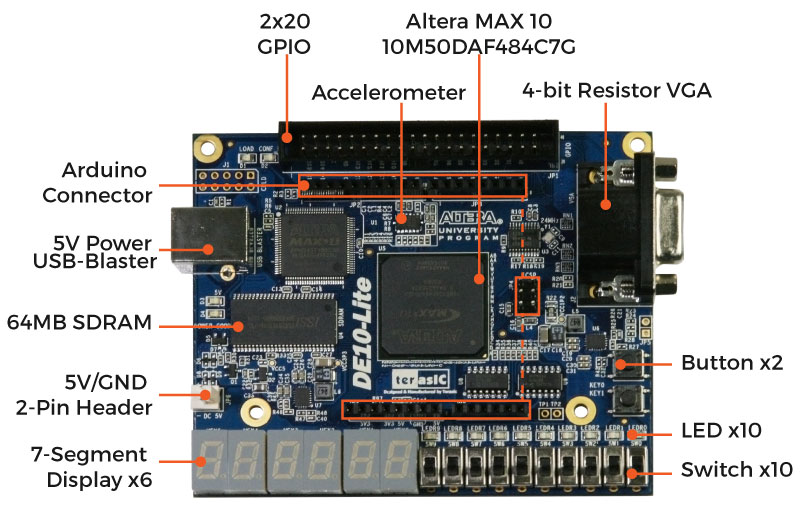

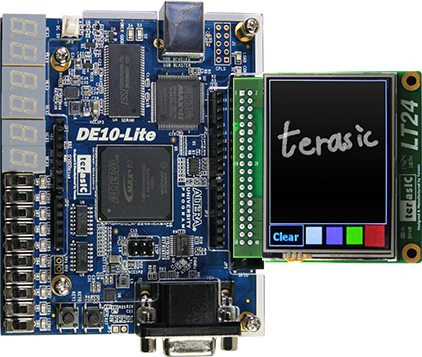

【DE10-Lite】TERASIC友晶 DE10-Lite Board

- 产品型号: DE10-Lite

- 产品品牌: TERASIC友晶科技/Intel FPGA

- 产品规格: MAX 10 10M50DAF484C7G Device

- 产品价格: 欢迎咨询采购,量多优惠多,提供完善的售后保障和支持!

- 咨询热线:18062095810

Terasic DE10-Lite is a cost-effective Altera MAX 10 based FPGA board. The board utilizes the maximum capacity MAX 10 FPGA, which has around 50K logic elements(LEs) and on-die analog-to-digital converter (ADC). It features on-board USB-Blaster, SDRAM, accelerometer, VGA output, 2x20 GPIO expansion connector, and an Arduino UNO R3 expansion connector in a compact size. The kit provides the perfect system-level prototyping solution for industrial, automotive, consumer, and many other market applications.

The DE10-Lite kit also contains lots of reference designs and software utilities for users to easily develop their applications based on these design resources.

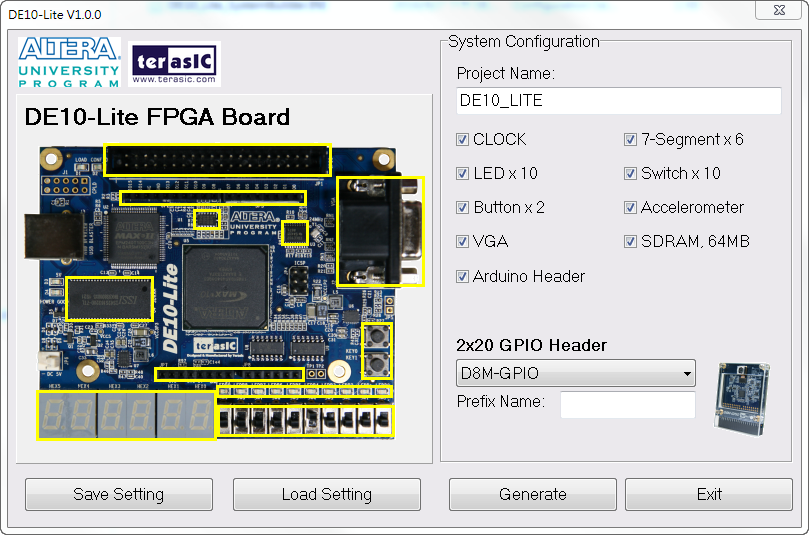

This board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects. The following hardware is provided on the board:

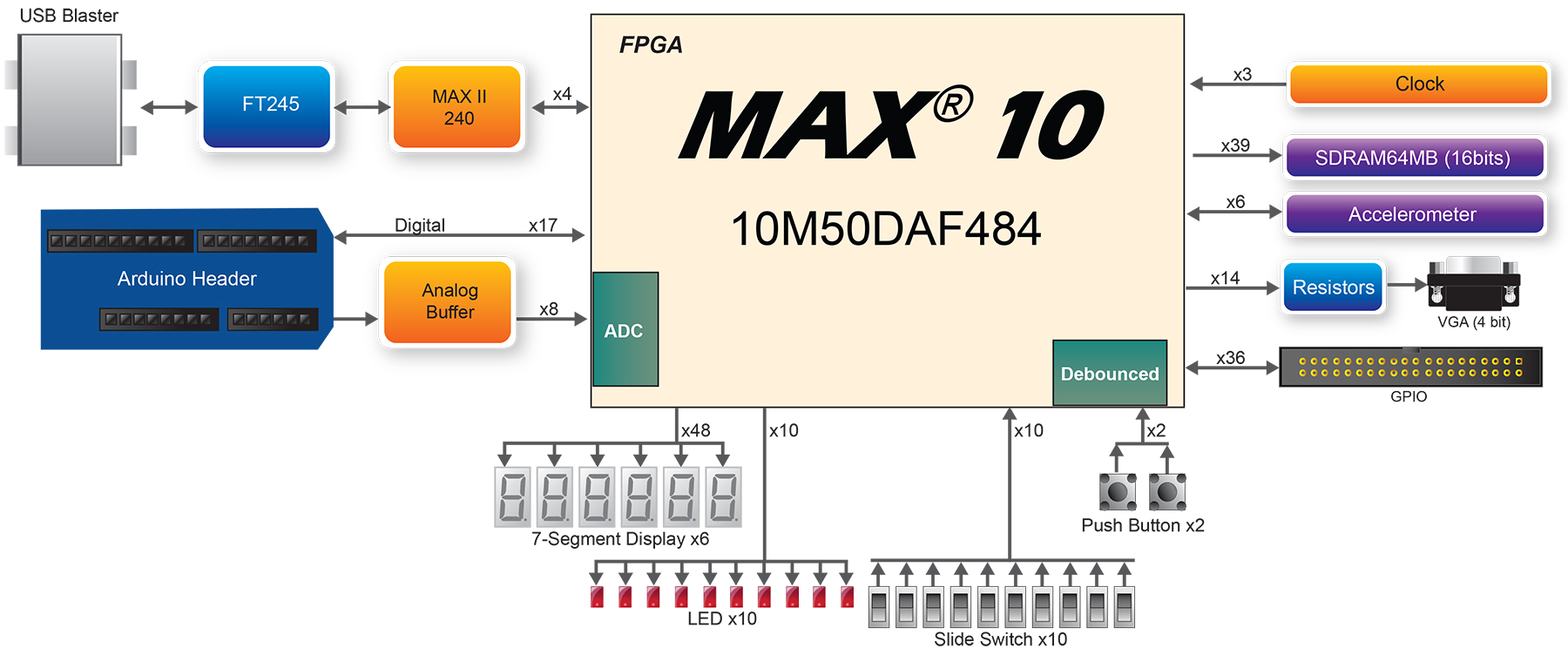

FPGA Device

- MAX 10 10M50DAF484C7G Device

- Integrated dual ADCs, each ADC supports 1 dedicated analog input and 8 dual function pins

- 50K programmable logic elements

- 1,638 Kbit M9K Memory

- 144 18 × 18 Multiplier

- 4 PLLs

Programming and Configuration

- On-Board USB Blaster (Normal type B USB connector)

Memory Device

- 64MB SDRAM, x16 bits data bus

Sensor

- Accelerometer

Expansion Connectors

- One 2x20 GPIO Connector(voltage levels: 3.3V)

- Arduino Uno R3 Connector, including six ADC channels.

Display

- 4-bit Resistor VGA

Switches/Buttons/LEDs/7-Segment Display

- 10 LEDs

- 10 Slide Switches

- 2 Push Buttons

- Six 7-Segments Display

Power

- 5V DC input

Block Diagram of the DE10-Lite Board

Connectivity

-

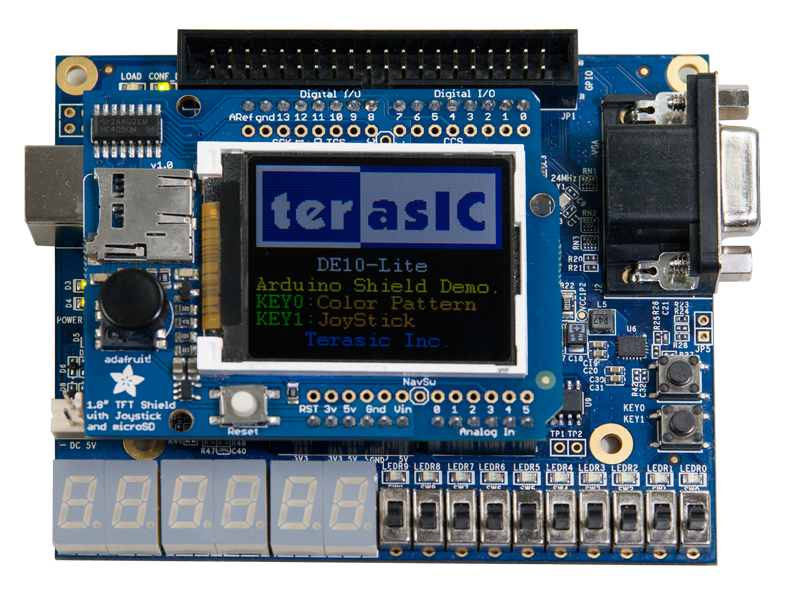

Connect with MTL2

-

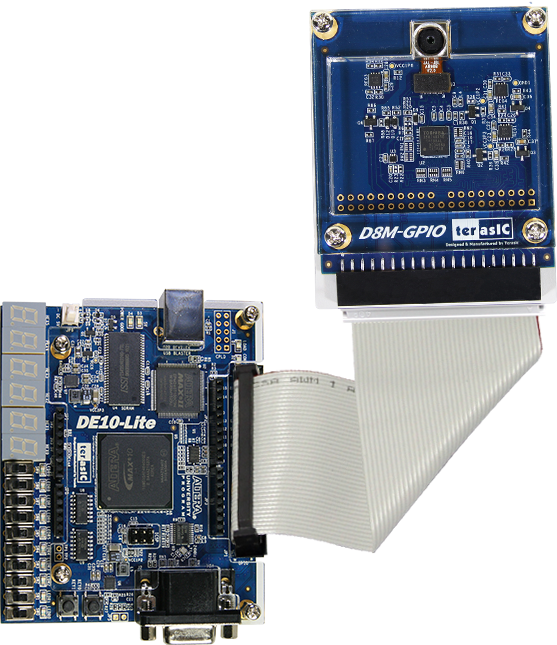

Connect with D8M-GPIO

- Connect with D5M

- Connect with Arduino Shield

- Connect with LT24

| No | 产品名称 | 售价(RMB) |

|---|---|---|

| 1. |

[DE10-Lite] DE10-Lite Board

产品编号: P0466

重量: 200g 重量: 200g |

xxx |

| 2. |

[DE10-Lite] DE10-Lite Board (教育版)

产品编号: P0466

重量: 200g 重量: 200g |

xxx |

Documents

标题

版本

档案大小(KB)

新增日期

下载

DE10-Lite User Manual

1.4

6103

2017-01-24

Daughter Card Demonstrations

标题

版本

档案大小(KB)

新增日期

下载

D8M-GPIO

2017-05-18

LT24

2016-09-19

MTL2

2016-09-19

CD-ROM

标题

版本

档案大小(KB)

新增日期

下载

DE10-Lite CD-ROM

2.0.1

2017-08-14

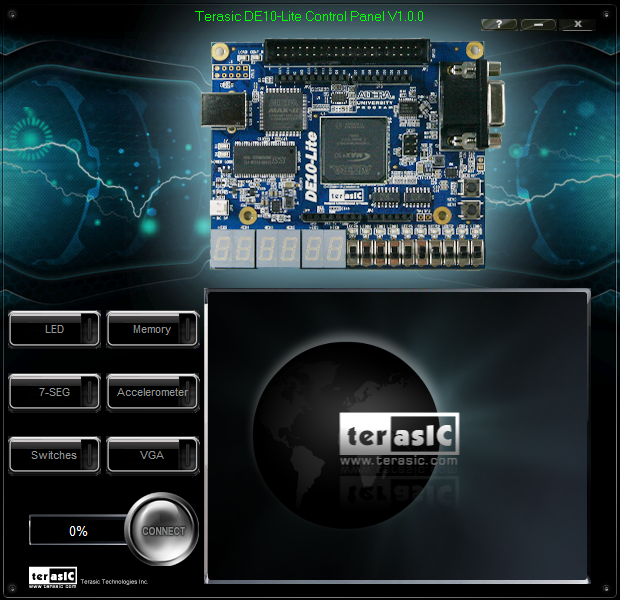

ControlPanel

1.0.2

2017-01-24

Quartus Download

15.1.2

2016-06-21

3D-Printer-Case

标题

版本

档案大小(KB)

新增日期

下载

Top cover

106

2016-08-18

Bottom cover

33

2016-08-18

友晶科技所发表之范例程式码,基於免费分享之原则,不提供任何形式的讲解或修改。如需进一步范例程式码讲解或修改的协助,我们将转至 "设计服务部门" 评估。

本授权条款允许使用者於使用所有友晶及 Altera 开发板时,得以重制、散布、传输以及修改友晶科技提供的源码,但不得为商业目的之使用。使用时必须於引用处表彰友晶科技 (Terasic Inc.) 之商号。

Documents

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| DE10-Lite User Manual | 1.4 | 6103 | 2017-01-24 |

|

Daughter Card Demonstrations

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| D8M-GPIO | 2017-05-18 | |||

| LT24 | 2016-09-19 | |||

| MTL2 | 2016-09-19 |

CD-ROM

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| DE10-Lite CD-ROM | 2.0.1 | 2017-08-14 | ||

| ControlPanel | 1.0.2 | 2017-01-24 | ||

| Quartus Download | 15.1.2 | 2016-06-21 |

3D-Printer-Case

| 标题 | 版本 | 档案大小(KB) | 新增日期 | 下载 |

|---|---|---|---|---|

| Top cover | 106 | 2016-08-18 |

|

|

| Bottom cover | 33 | 2016-08-18 |

|

本授权条款允许使用者於使用所有友晶及 Altera 开发板时,得以重制、散布、传输以及修改友晶科技提供的源码,但不得为商业目的之使用。使用时必须於引用处表彰友晶科技 (Terasic Inc.) 之商号。

Example Designs in System CD

- Factory Default Code

- SDRAM Test in Nios II

- SDRAM Test in Verilog

- VGA Pattern

- Accelerometer Level

- Accelerometer Rock

DE10-Lite Control Panel

Allows users to access various components on the DE10-Lite board from a host computer.

DE10-Lite System Builder

This tool will allow users to create a Quartus II project on their custom design for the DE10-Lite board with the top-level design file, pin assignments, and I/O standard settings automatically generated.

Other course resources you might interested:

School:Cornell UniversitySenior Lecturer - Bruce Land