产品展示

-

- Intel FPGA-Altera Agilex母板 Intel FPGA-Altera Stratix母板 Intel FPGA-Altera Arria母板 Intel FPGA-Altera Cyclone母板 Intel FPGA-Altera MAX母板 Intel FPGA-Altera 多媒体子板 Intel FPGA-Altera 界面转换子板 Intel FPGA-Altera 影像显示类子板 Intel FPGA-Altera 网路子板 Intel FPGA-Altera 类比/数位转换子板 Intel FPGA-Altera RF子板 Intel FPGA-Altera机器人套件 Intel FPGA-Altera USB Blaster Intel FPGA-Altera配件 FPGA|DSP|ARM|EDA|SOC教学实验箱 TI系列-C6000 DSP|ARM TI系列-C5000 DSP TI系列-C2000 DSP TI系列-DaVinci|Sitara TI系列-仿真器

推荐产品

- FPGA综合实验台 HC-STD-M

- 【DPO7254C】Tektonix泰克 高级信号分析示波器

- 【TMS320C6655/57】Tronlong创龙TL665xF-EasyEVM开发板

- HKMX-30型 十字路口交通信号灯实训装置

- 【SFP】TERASIC友晶SFP-HSM子板

- 【XAUI-SFP】DUAL XAUI TO SFP+ HSMC BOARD

- 【DK-DEV-1SGX-H-A】Intel Stratix 10 GX FPGA Development Kit

- 【TDS2024C】Tektonix泰克 200MHz示波器

- 【6221】Tektonix泰克 精密电流源

- 【DS1202Z-E】RIGOL普源 200MHz数字示波器

咨询热线:

18062095810

邮件: wangting@whhexin.com

电话:027-87538900

地址: 湖北·武汉·鲁巷·华乐商务中心1006

基于FPGA口袋式计算机组成原理实验系统

- 产品型号: HC-V

- 产品品牌: TERASIC友晶科技/Intel FPGA

- 产品规格: Cyclone IV E系列

- 产品价格: 欢迎咨询采购,量多优惠多,提供完善的售后保障和支持!

- 咨询热线:18062095810

口袋型实验系统是新一代计算机组成原理实验系统,它采用了全新的设计思路和实现技术,使得它硬件成本低、可靠性高、使用寿命长,而且功能强大、灵活性和适应性都非常强。

口袋型实验系统是新一代计算机组成原理实验系统,它采用了全新的设计思路和实现技术,使得它硬件成本低、可靠性高、使用寿命长,而且功能强大、灵活性和适应性都非常强。

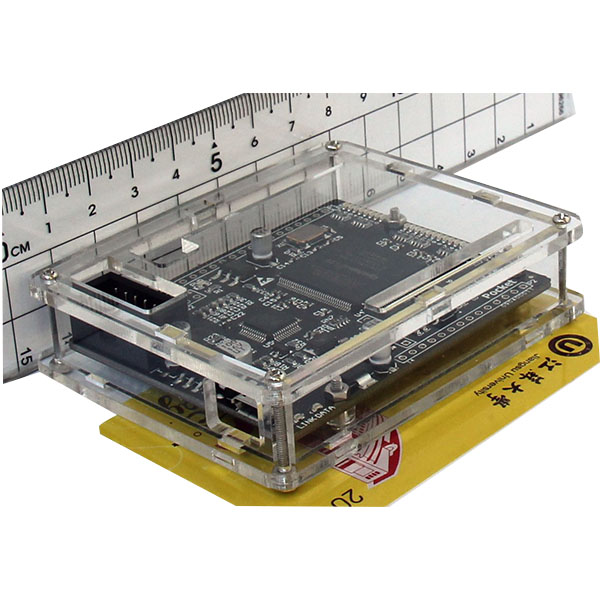

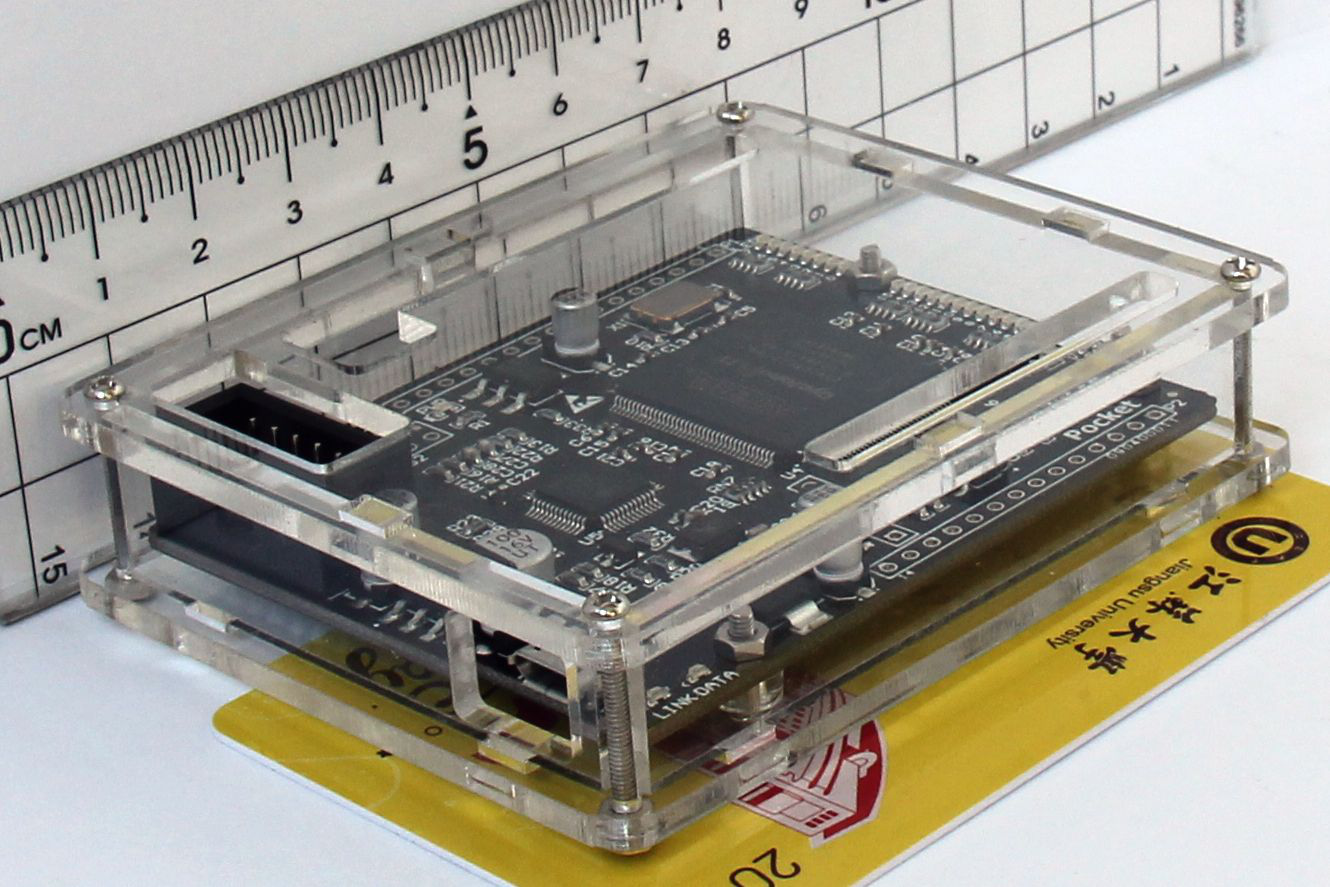

实验系统包括口袋实验板和虚拟实验软件两部分。口袋实验板仅有信用卡大小,采用Altera Cyclone IV E系列EP4CE6E22C8芯片,实验板没有开关、按键等操作元件,需要通过配套软件的虚拟实验界面进行实验操作。

口袋实验板适合于提供给学生个人,不受实验室时间限制地完成实验或进行课外拓展。

基本功能

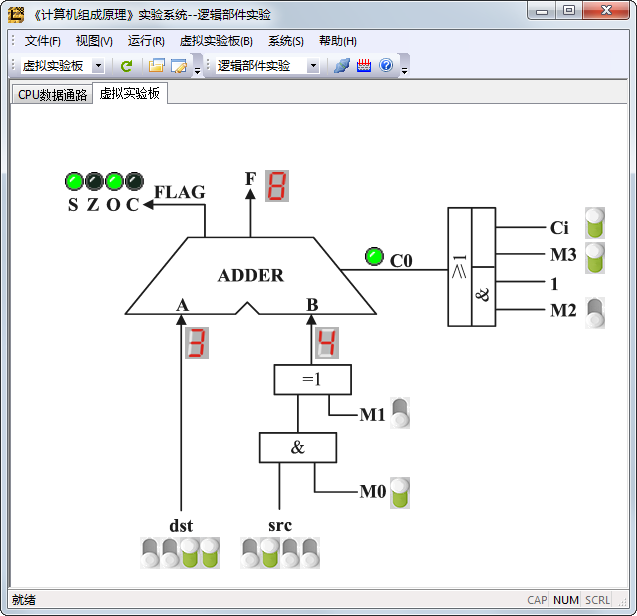

可完成“数字逻辑”和“计算机组成原理”课程的逻辑电路实验;

可完成“计算机组成原理”和“计算机系统结构”课程的CPU实验;

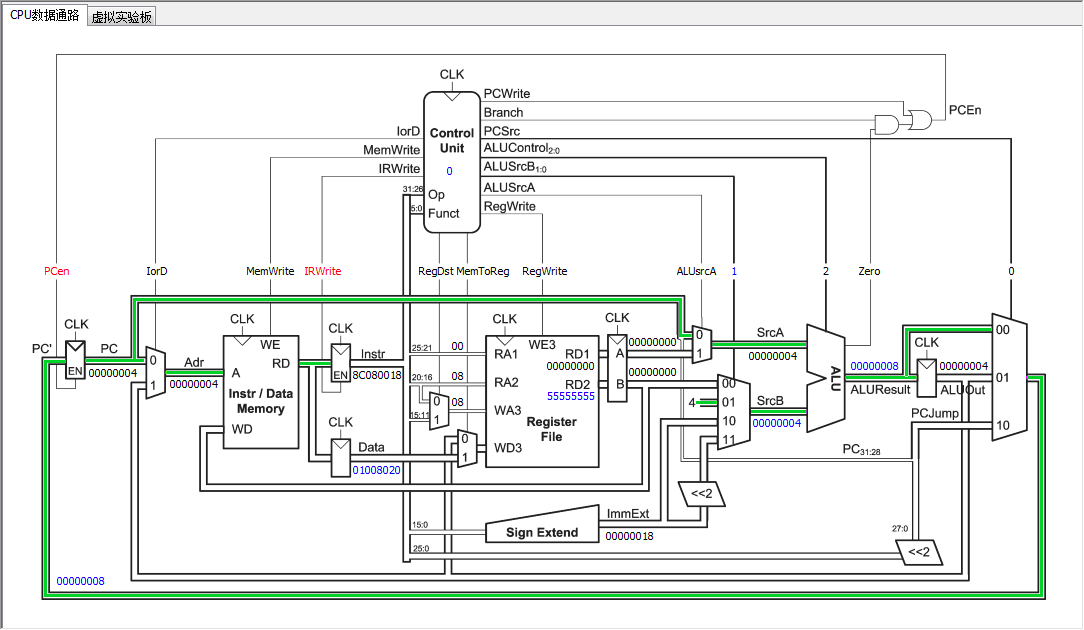

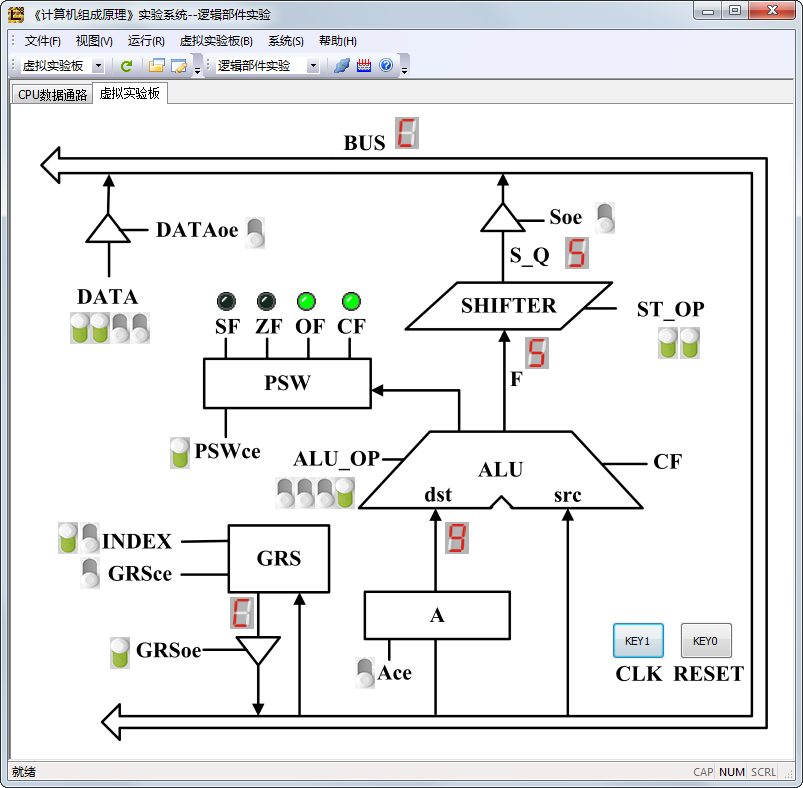

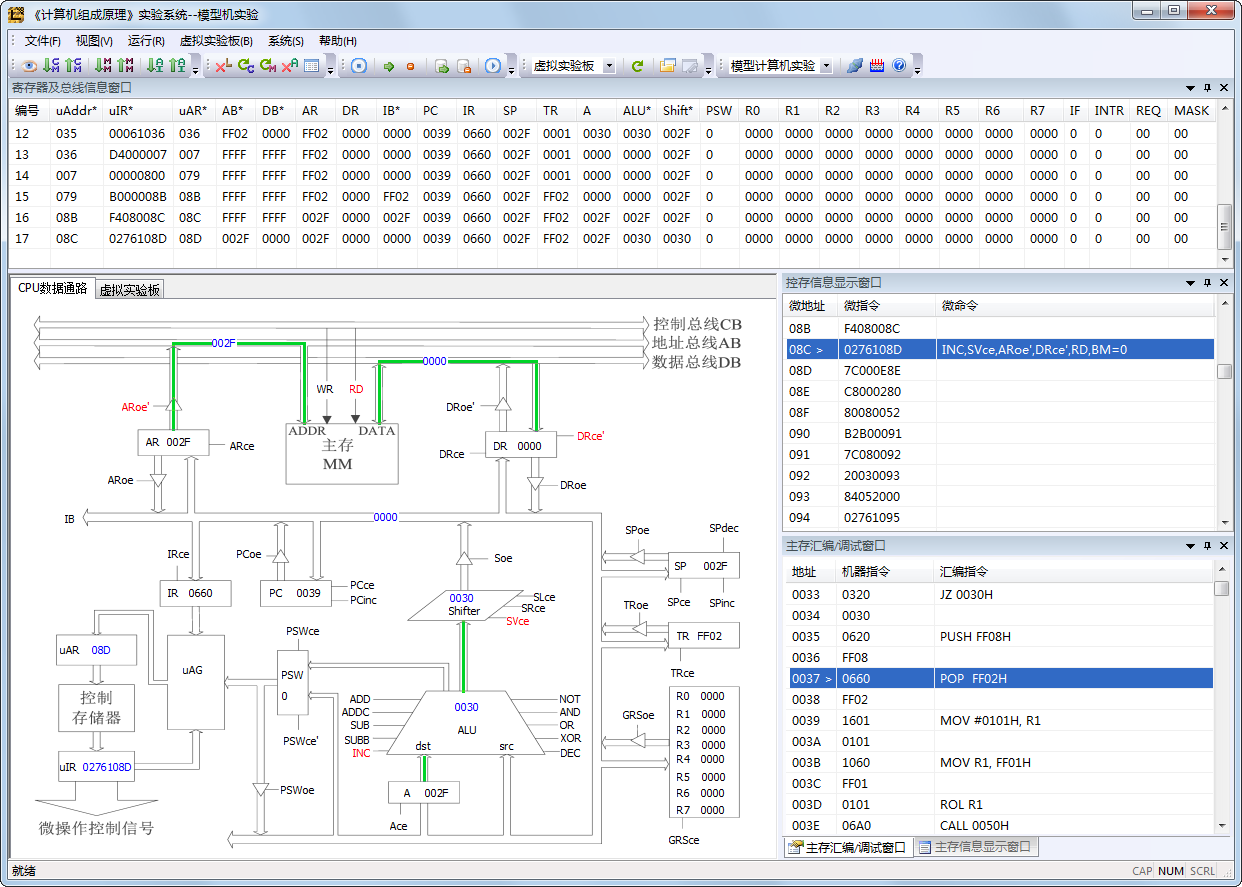

实验过程可视化:在虚拟实验板上操作,以信息流方式显示CPU的指令执行过程;

支持用户自定义实验内容、自定义虚拟实验板、自定义CPU数据通路。

配套《计算机组成原理实践教程》由清华大学出版社出版发行(肖铁军主编,ISBN:9787302382805),包括10个实验项目(如运算器、高速缓存、微控制器、中断系统等)和2个课程设计项目(CPU设计、微程序设计)。

主要特点

基于FPGA的实验技术,可以结合教学内容设计实验,便于和课堂教学相配套,改变课堂讲一套、实验做另外一套的状况。既可以支持设计型、创新型实验,也可用设计好的电路进行原理验证型实验,便于实施多层次的实验教学。

不仅具有真实感的虚拟实验板,并且独创基于原理图的虚拟实验板,使学生将注意力集中在实验原理上,无需将精力消耗在开关等元件与原理的对应上,提高实验效率。系统提供虚拟实验板设计工具,用户可为自己的实验定制虚拟实验界面。

学生所有的操作都是在计算机的虚拟界面上完成,甚至不需要实验板具有实际的开关按键、指示灯数码管等元件,从而极大地降低了实验板的故障率和日常维护成本。

模型机实验可动态显示实验CPU的运行状态。CPU内部状态通过调试电路传递到用户界面,以数据记录和图形化两种形式显示。高亮显示当前有效的控制信号、变化的数值以及信息流动,方便学生调试设计,加深对指令执行过程的理解。也可用于教学演示。模型机的调试支持微指令单步、微指令断点、指令单步、断点、全速等运行方式。可通过软件界面输入、查看和保存控存、主存内容。

目前已设计微程序控制的JUC-II(上图)和基本的多周期MIPS(下图)等三种CISC或RSIC实验CPU;并且用户可以扩充自己的实验CPU,只需要通过特定的脚本描述CPU的特性即可由实验调试系统可视化显示。