热点资讯

咨询热线:

18062095810

邮件: wangting@whhexin.com

电话:18062095810

地址: 湖北·武汉·鲁巷·华乐商务中心1006

SoC FPGA初学者的天籁之选-DE10-Nano

DE10-Nano 是一款 Cyclone V 系列的 SoC FPGA 开发板,它拥有 110K 逻辑单元和 ARM Cortex-A9 双核处理器,小巧平价却不失质感,素有“麻雀虽小,五脏俱全”之称。此外,DE10-Nano 开发板还提供了海量免费的培训材料和支持包。这无疑是 SoC FPGA 初学者们的天籁之选,更让FPGA进阶者们在开发设计时如虎添翼!

应用案例:DE10-Nano助力Mandelbrot分形图像算法

Terasic DE10-Nano 是一款 Cyclone®V 系列的 SoC 开发板,Cyclone®V SoC FPGA 是在 FPGA 的架构中集成了基于双核 ARM Cortex-A9 硬核处理器(HPS)的系统,其中 FPGA 与 HPS 之间通过 AXI 总线高速互联。因此,这种架构既具备了 ARM 处理器灵活高效的数据运算和任务处理能力,又集成了 FPGA 高速并行处理及低功耗的优势。使用该异构架构来加速复杂的算法,有着得天独厚的的优势。

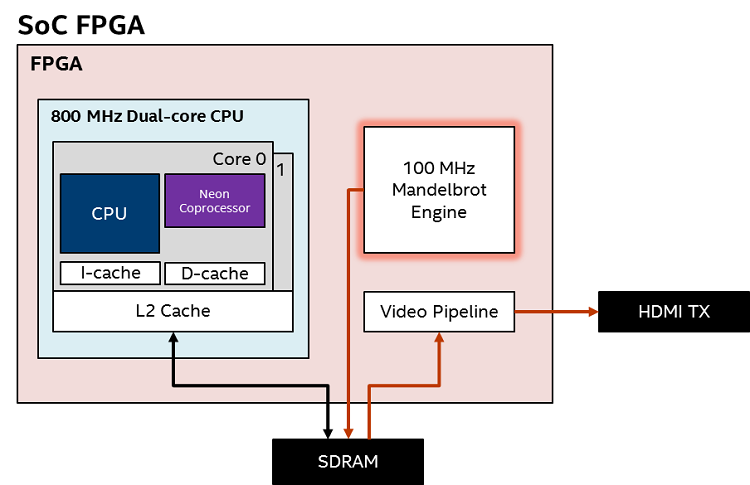

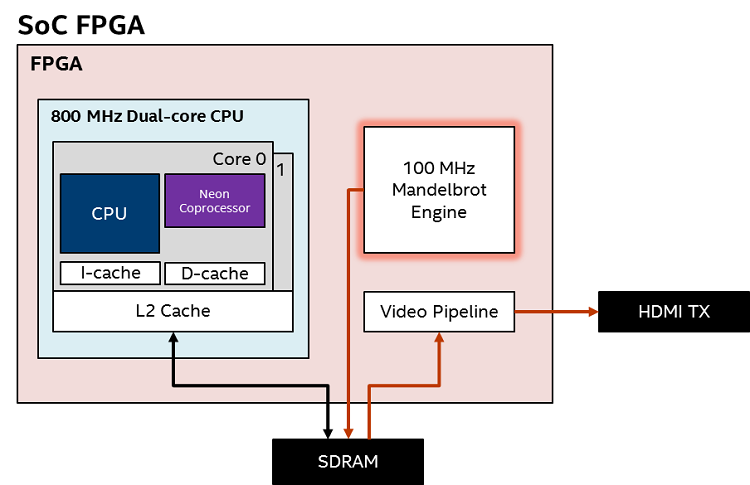

我们既可以选择 ARM CPU 单独运行,也可以切换至使用 FPGA 来进行加速(如下图所示)。当使用 FPGA 加速 Mandelbrot 分形算法时,系统将通过 Terasic DE10-Nano 上的 FPGA 硬件架构实现的 Mandelbrot 引擎来生成分形图像,接着将图像数据写入外部 SDRAM 缓冲,再通过实现的 Video Pipeline 将图像显示到 HDMI 显示器。

我们既可以选择 ARM CPU 单独运行,也可以切换至使用 FPGA 来进行加速(如下图所示)。当使用 FPGA 加速 Mandelbrot 分形算法时,系统将通过 Terasic DE10-Nano 上的 FPGA 硬件架构实现的 Mandelbrot 引擎来生成分形图像,接着将图像数据写入外部 SDRAM 缓冲,再通过实现的 Video Pipeline 将图像显示到 HDMI 显示器。

为了对比在 FPGA 硬件和 ARM 端软件上实现的 Madelbrot 分形算法的性能,分别采用时钟频率为800MHz 的 ARM CPU 和100MHz 的 FPGA。不难发现:使用 CPU 时,显示屏的更新速度要慢得多,且CPU 利用率为99%或更高,这无疑会占用大量 CPU 处理资源。而虽然 FPGA 的时钟频率更低,但实际更新速度却更胜一筹,并且此时 CPU 的使用率也降低至4%—6%左右。这个现象说明了将FPGA用于复杂算法的两个主要优点:

1. FPGA 的运行速度更快。由于 FPGA 的并行性和并发性的优势,在 FPGA 内部,不同逻辑功能之间的多个不同功能的模块可以同时独立的进行计算,还可以利用 Pipeline 进行流水线操作,让流水线上的每个阶段都处于满负荷运行状态,来处理不同的需求。

2. FPGA 可以有效的减轻 CPU 中复杂算法的负担,从而将 CPU 释放给其他任务,例如运行网络堆栈,管理文件系统或与其他主板资源接口,在获得更高性能的同时让 CPU 发挥更多优势。